PCIE的阻抗控制,到底是选择85还是100欧姆好?

发布时间:2023-12-22 13:46

高速先生成员--周伟

我们经常遇到很多系统通过高速连接器相连,信号按照Pcie3或者Pcie4的协议来走线,往往很多连接器的阻抗通常是100ohm的标准,而Pcie3或者Pcie4按照协议或者芯片要求却是85ohm的标准,那么这个时候我们的线路阻抗到底是按照85还是100欧姆会比较好呢?

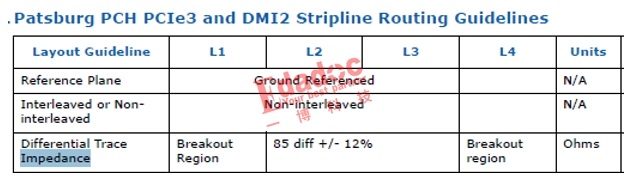

如下是关于线路阻抗的一些芯片要求或者协议要求。

总结起来就是Pcie3.0以下是100ohm,Pcie3或者以上就是85ohm的标准,速率越高,阻抗的公差要求就越严格。

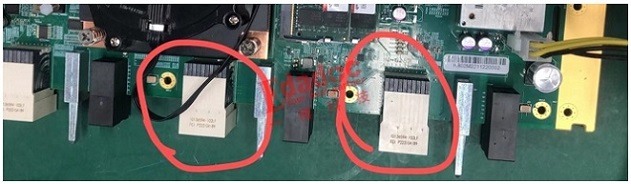

现在我们的一个客户就遇到了一个上面的实际问题。客户的系统是由CPU板和FPGA板组成,其中CPU板上面有4个高速连接器分别与FPGA板上的一个连接器对接,中间的信号使用Pcie3.0协议,后面可能会升级支持到Pcie4.0协议,而中间的连接器是常规背板连接器,如下图所示:

然后客户反馈的问题如下:

同时测试的眼图也比较差,眼睛几乎快睁不开了,一副没睡醒的样子。

对应CPU板的位置如下图所示:

同一个板子,其中有两个连接器对接的容易出问题,另外两个没发现什么问题,出现这种情况,我们的处理措施是先看看PCB设计,然后根据设计情况再看下一步的安排。

打开PCB设计文件,查看Card3连接器上TX0和Card4连接器上RX1的走线,分别如下所示:

Card3连接器上TX0在底层,连接器处也做了反盘挖空处理,BGA处没有优化,和其他的信号一起走过去的,优化方式也是差不多,没有理由单独这根信号比较差;

Card4连接器上RX1在Art12层,除BGA处没有优化外其它也都有相应的优化,只是这根信号是在一组走线的边沿。从设计来看也没有太多问题,比较常规。

从设计来看确实看不出明显的问题,事出反常必有妖,了解我们高速先生套路的童鞋们肯定知道我们下一步的操作,那就是是骡子是马,拉出来溜溜—实物板测试一下阻抗,看看阻抗到底有什么区别。

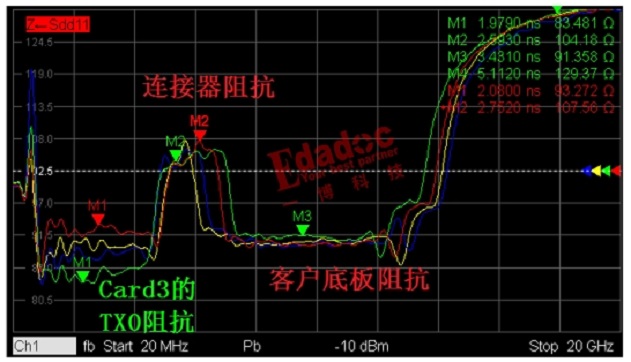

Card3接底板的系统阻抗

从Card3的系统阻抗来看,首先问题最大的连接器阻抗偏高,最高到了107ohm,其次出问题的TX0信号在Card3上的阻抗最低,在83ohm左右,而底板的阻抗在90~91ohm左右,此时从反射角度来看,TX0线路上的阻抗和连接器的阻抗偏差最大;

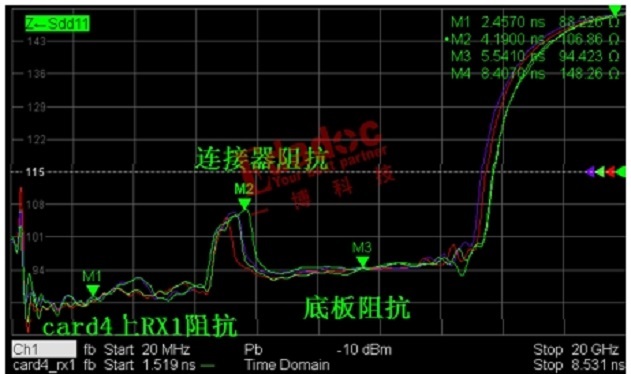

Card4接底板的系统阻抗

从Card4的系统阻抗来看,问题最大的仍然是连接器阻抗比较高,最高到了107ohm左右,最高阻抗正好是出问题的RX1信号,Card4整体的阻抗都在88ohm左右,而底板的阻抗在94ohm左右,此时从反射角度来看,RX1线路上的阻抗和连接器的阻抗偏差最大;

从两块板子系统阻抗的测试结果来看,都有几个共性的特点:首先连接器阻抗偏高,其次底板阻抗控制在92~94ohm左右,而子卡不管是Card3还是Card4,阻抗应该是按照85ohm的阻抗要求来管控的,整体阻抗都在90ohm以下,另外出问题较多的两根信号在系统上最低和最高阻抗的偏差最大,也就是反射最大。

看到这里,我们的问题来了:

从解决问题的角度出发,Card3和Card4连接器所在的子板怎么设计可能可以解决目前的问题?欢迎大家畅所欲言。