深入分析时钟信号走在PCB的表层到底有什么风险?

发布时间:2024-02-27 13:31

高速先生成员--黄刚

首先不要质疑前辈们的话,时钟信号的确最好不要放在表层,哪怕是你认为很低频的时钟,像25MHz、100MHz、156.25MHz这些时钟。做多了高速串行信号设计的工程师们可能只会觉得高速信号不应该放在表层,原因给出得也非常合理,例如表层的阻抗加工误差会比较大,高速信号对阻抗的要求很高;又或者表层的绿油损耗很大,高速信号对损耗的要求也很高等等,似乎都觉得速率高的信号才值得应该重视。

的确,高速信号有着它们的设计难点,但是如果你认为一个100MHz的时钟信号就可以随便走线都没问题的话,那可能也有失偏颇了!高速先生马上就告诉大家一个“残酷”的事实,100MHz的时钟信号也可以是很“高速”的信号。时钟的频率低不代表没有更高频的能量,频率低只是时钟信号外在的一个掩饰,它最可怕的地方其实是在。。。它的上升下降沿!

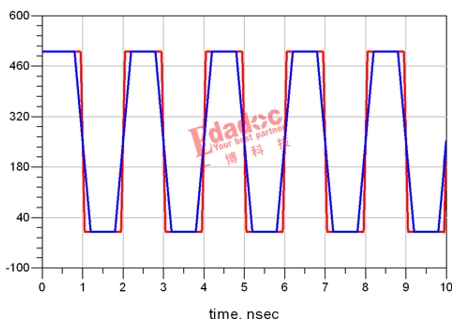

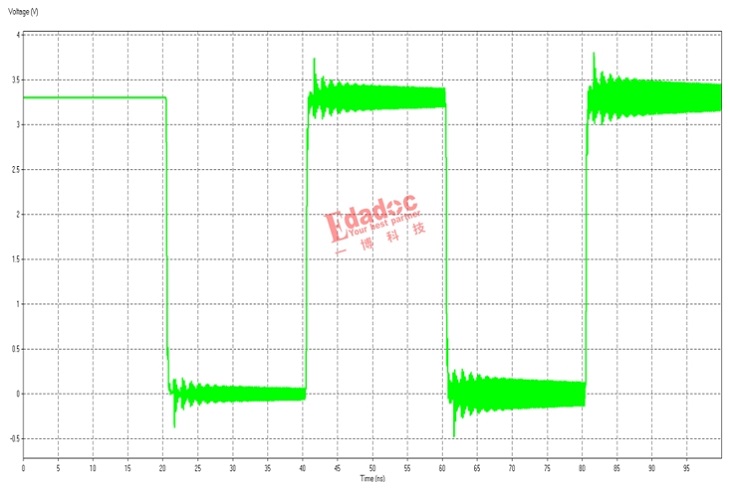

我们可以看这两个频率一样的时钟信号,什么叫频率一样,应该不用过多说明了吧。

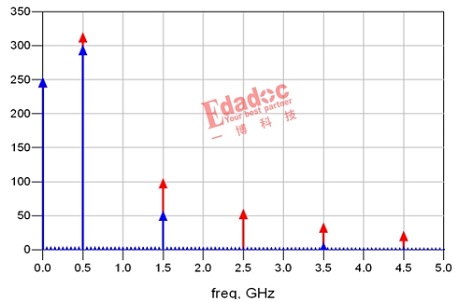

它们的差别只是在上升/下降沿的时间不同。没错,就是因为这个差别,它们包含的高频分量就差很老远了。红色的信号上升/下降沿很快,从频率分量看,它的高频分量更为丰富,而蓝色的时钟信号则相反。所以,它们可以叫做频率相同,但是高速程度不同的时钟信号。

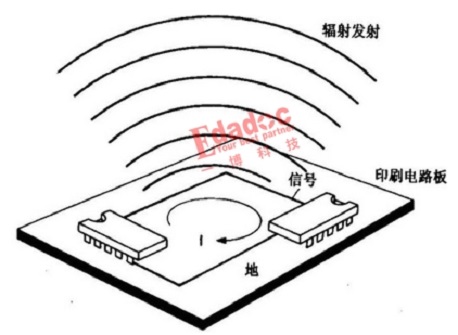

那时钟高频分量多有什么风险呢?高频分量多的话能量就很容易不受控制的到底乱窜,如果刚好加上时钟信号走在表层的话,整个效果就像下面这个场景一样了。

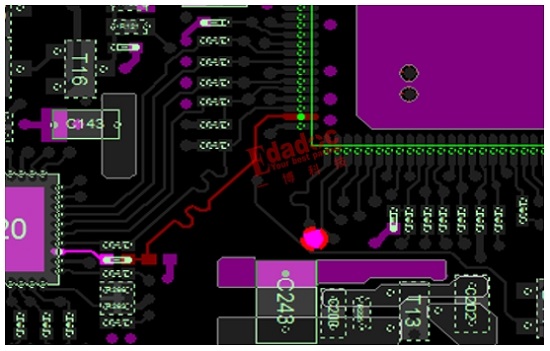

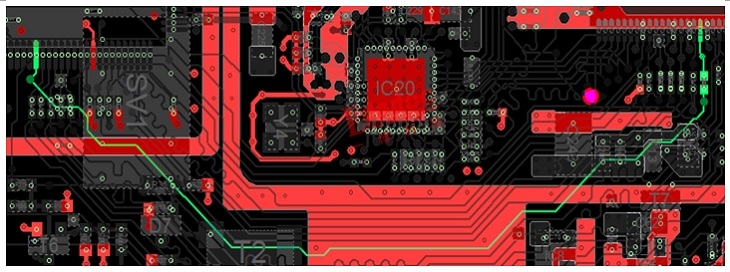

对,铺垫了半天,今天我们要分析的就是时钟信号的EMI辐射问题。上面都是定性的去分析,下面我们将以一个具体的PCB设计案例来进行定量的展示。一个很简单的时钟信号走线设计,由于两个芯片距离很近,时钟的频率也只有25MHz,那设计工程师就直接表层走过来就完事了!

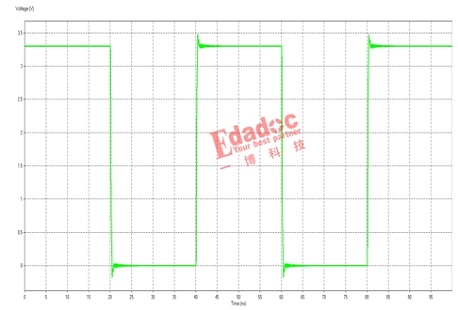

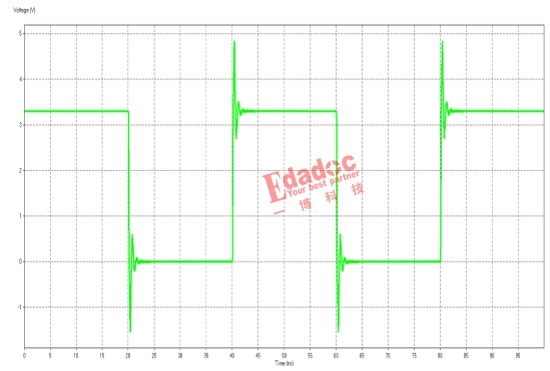

我们拿到收发芯片的仿真模型,去仿真这条短时钟链路的波形,由于有一个源端的串阻进行端接,加上时钟频率也就25MHz,因此波形质量没太多的问题。

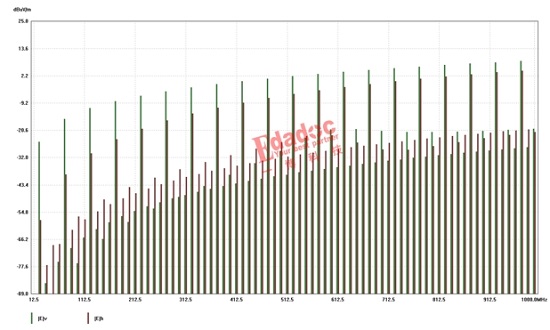

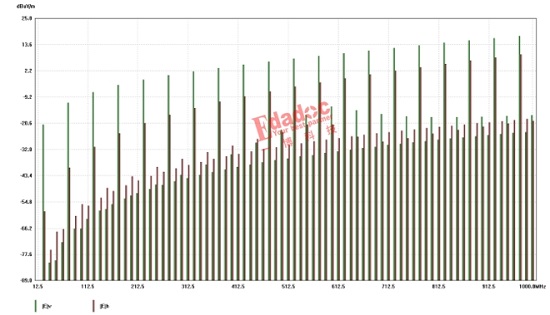

除了仿真时钟信号的波形外,高速先生还顺带仿真了下时钟信号对这块PCB板在远场时的EMI辐射。仿真结果如下:可以看到,虽然只是25MHz的时钟,但是对远场EMI的影响可以cover到10倍以上的基频。当然了,这个结果其实也是满足EMC指标的,毕竟走线很短,而且还有端接。

那看起来就是没啥问题嘛!高速先生从来都很严谨,于是我们就对比同一块板子上另外一根同频率但是走线内层的时钟信号,这根信内层信号时钟还更长。

同样的,我们对这根内层时钟进行仿真,在良好端接的情况下,时钟信号的波形也是没问题的。

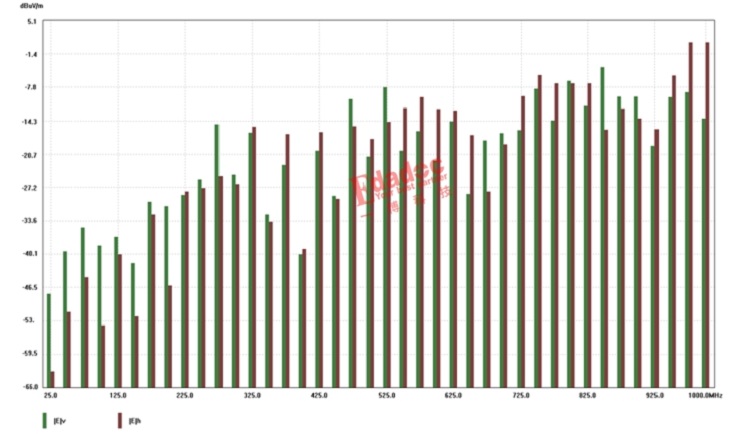

我们也进一步仿真下这根内层时钟的远场EMI结果,会发现这根长度长好几倍的内层时钟的EMI辐射量级居然还比表层的这根这么短的时钟在量级还小差不多10db。

做到这里其实应该能说明问题了,但是高速先生还额外再仿真一种case,那就是这根短的表层时钟走线如果端接不理想或者没端接的时候呢?波形质量变差的同时对EMI辐射的影响会不会加剧呢?那我们继续往下做,我们把这个PCB设计中的串阻不用,也就是直接短路,不加串阻的情况下,由于反射没有被端接,接收端的波形会产生过冲,在我们的预料之中。

关键我们要看在这样的情况下,EMI的辐射情况是怎么样的?从下面的结果可以看到,在时钟信号端接不好的情况下,不仅会影响信号质量,而且会产生更多的高频分量,EMI的辐射量级对比端接理想的情况下,居然足足恶化了10db,不敢想象,如果走线长度更长的话,恶化的程度估计就更厉害了。

最后总结一下吧,时钟信号的上升沿就是一个难点所在,除了对上升沿本身的单调性要求外,上升时间如果很小的话,就会出现上面说的信号过冲和EMI辐射的恶化。有的产品不仅要重视信号质量本身,对EMC的要求也很高。因此不要小看这百来MHz的时钟信号,有一些设计经验还是应该去重视和遵循的哈!