端接电阻没选对,DDR颗粒白费?

发布时间:2024-03-04 14:10

高速先生成员--姜杰

端接可以解决很多反射问题,如果还有问题,有没有一种可能是端接电阻阻值没选对?

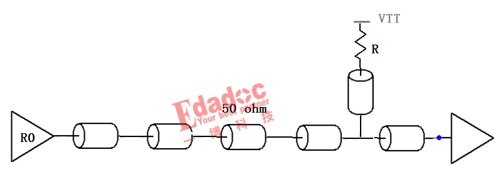

对于点到点的拓扑,末端并联电阻的阻值比较容易选择,端接电阻阻值R与传输线特征阻抗一样即可。

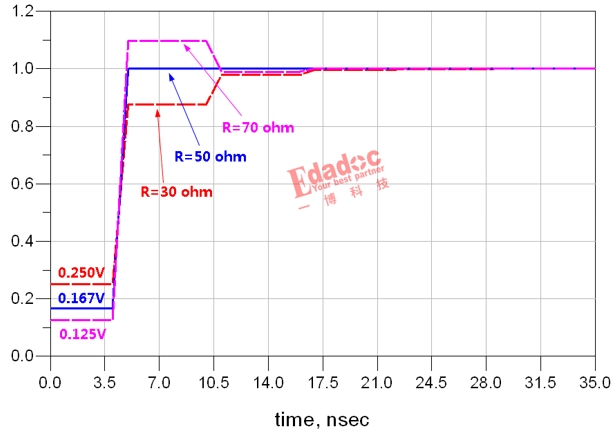

VTT为1V时,端接电阻R分别取30ohm,50ohm,70ohm的接收端电压如下图:

可以发现,R与传输线特征阻抗同样都是50ohm时,接收端信号基本没有反射。原因是接收器输入阻抗通常很高,从信号的角度看,传输到末端的信号感受的阻抗就是端接电阻的阻值,R与传输线特征阻抗的匹配消除了阻抗突变引起的反射。

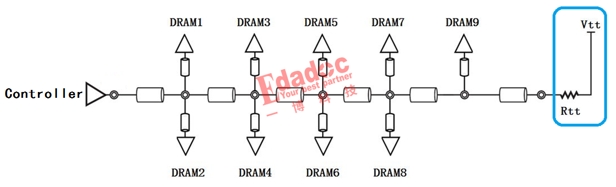

不幸的是,目前的绝大多数DDR的地址控制信号都是一驱多的拓扑,于是,问题开始变的复杂。

明明DDR的数据信号速率更高,为啥要更关注DDR的地址控制信号?数据信号一般都是点到点的拓扑,而且大多有片上端接(ODT),走线拓扑简单加上端接加持,信号质量通常都比较有保障。而DDR的地址控制类信号的设计难度在于其拓扑的复杂性,一驱多的走线拓扑对信号质量的影响太大,即便速率相比数据信号减半。

为了让大家对端接电阻的作用感受更加明显,我们选择了一个难度较大的案例:一驱九的DDR4地址信号,速率1600Mbps。

由于反射更容易在近端颗粒DRAM1/DRAM2处积累,该处的信号质量更容易成为瓶颈。

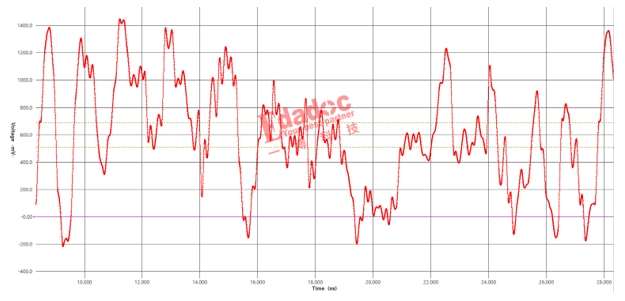

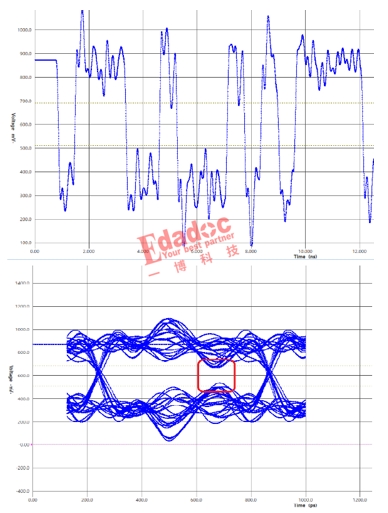

方便对比,先看看不加端接的近端DRAM1信号。

和预料的一样,波形是杂乱的,眼图是闭合的。

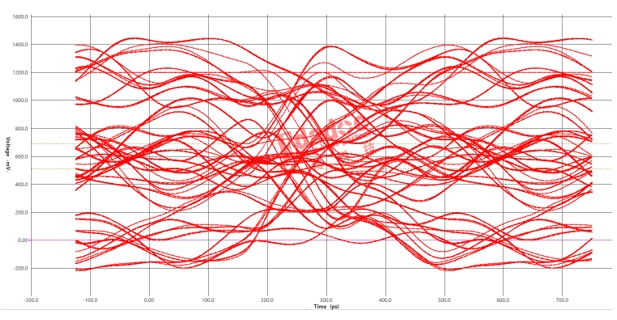

再来看看按照原设计的39ohm端接电阻,近端颗粒信号质量有什么变化。

显而易见,波形质量有了较大改善,眼睛也睁开了。但还是会有部分波形落在阈值电平(VIH:690mV;VIL:510mV)的区间内,这种情况下的时序大概率是Fail的。

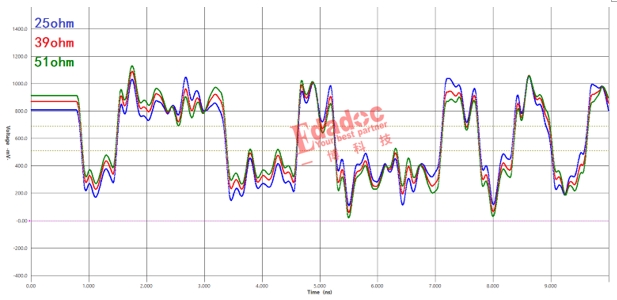

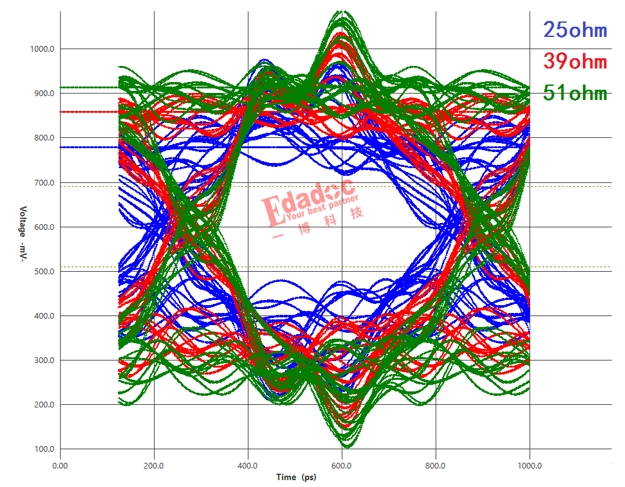

下面扫描三种端接电阻阻值:25ohm,39ohm和51ohm,近端颗粒信号的波形对比如下:

可以发现,按照这三种阻值的从大变小,信号质量是逐渐改善的。

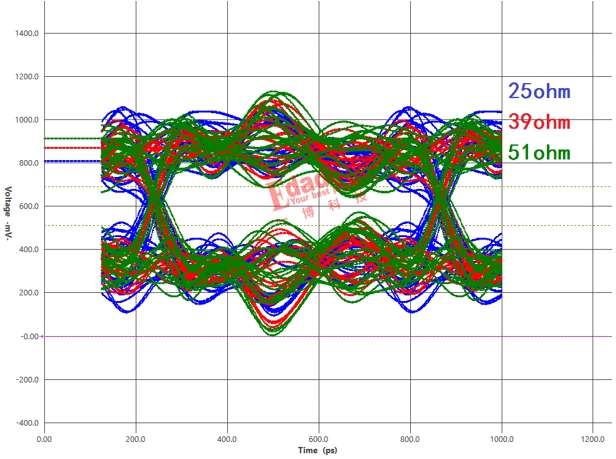

对眼图的睁开程度进行对比,这种趋势会看的更加明显。

为了能看的更清楚,将三个眼图在时间轴上展开进行对比。

以阈值电平(VIH:690mV;VIL:510mV)作为判决标准,25ohm端接电阻的眼图可以满足要求,另外两个则不达标。

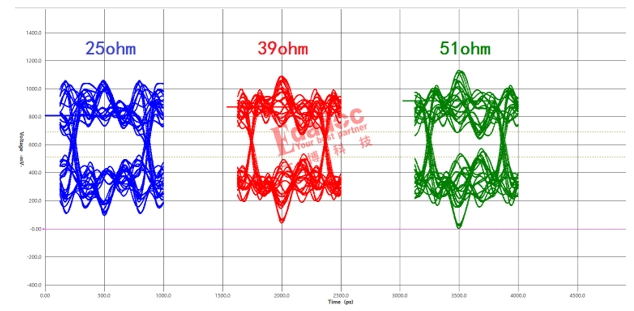

当然了,这是个多负载的拓扑,其它DDR上的信号也需要关注。通过对比,高速先生发现了一个有趣的现象,同样的阻值变化,远端颗粒DRAM9上的信号质量变化与近端颗粒正好相反。

好在远端DDR由于更靠近端接电阻,信号裕量更大,因此可以“损有余而补不足”,即便选择远端波形最差的25ohm,眼图也是可以满足阈值电平要求的。

那是不是所有的一驱多DDR地址控制信号,随着端接电阻阻值变化都有相同的趋势呢?仅通过这一个案例,高速先生也无法给出一般性的结论。唯一可以肯定的是:前途是光明的,道路是曲折的,阻值是不确定的。拓扑越复杂,速率越高,就越有必要通过仿真确定最优端接电阻阻值。

问题来了

大家知道的优化DDR地址控制信号质量的方法都有哪些?